This is a tutorial of FPGA design of convolutional encoder in Xilinx ISE. The convolutional codes are channel codes used in wireless communication such as space communication and broadcasting applications. It is a linear code but unlike block codes in which the inputs are grouped into blocks, in covolutional encoding the input stream are encoded sequentially. Another difference is that the convolutional encoder has memory whereas block encoder does not.

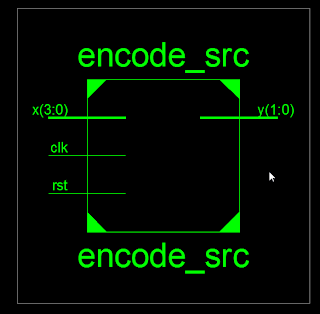

The following diagram shows the concept involved in the synthesis of encoder. The input binary signal x(n) enters the shift register at each clock frequency. At the output convolutionally encoded y(n) is produced also at the sampling frequency.

The verilog code for this convolutional encoder is shown below-

-------------------------------------------------------------------------------------------------------------

module encode_src(x,y,clk,rst);

input [3:0]x; //4-bit input data

output [1:0]y; //2-bit output data

input clk; //clock

input rst; //reset

reg [1:0]y;

reg [3:0]ff0;

reg ff1,ff2;

always@(posedge clk, posedge rst)

begin

if(rst)

begin

y <= 2'b0;

ff1 <= 1'b0;

ff2 <= 1'b0;

ff0 <= x;

end

else

begin

ff1 <= ff0[0];

ff2 <= ff1;

y[0] <= (ff0[0]^ff2);

y[1] <= ff0[0]^ff1^ff2;

ff0 <= ff0 >>1;

end

end

endmodule-------------------------------------------------------------------------------------------------------------------

In the code x and y are the input and output. The input x is a 4 bit sequence and the output is a 2 bit sequence. clk and rst are clock and reset. The ff0, ff1 and ff2 are flip-flops. Within the always block the if-else procedural statement is applied such that first the reset(rst) is checked. If it is ON then output y, the flip-flop 1 and 2 are cleared and the input first bit is entered into the flip-flop 0. If it reset is not set then the first input entry is shifted into ff1, the content of ff1 into ff2, output y(0) and y(1) are calculated as y(0)= x(n)+x(n-2) and y(1)=x(n)+x(n-1)+x(n-2).

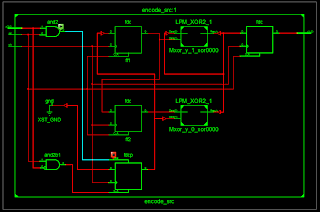

The corresponding Xilinx generated block diagram is shown below-

The following diagram shows the concept involved in the synthesis of encoder. The input binary signal x(n) enters the shift register at each clock frequency. At the output convolutionally encoded y(n) is produced also at the sampling frequency.

|

| Figure: Convolutional Encoder |

The verilog code for this convolutional encoder is shown below-

-------------------------------------------------------------------------------------------------------------

module encode_src(x,y,clk,rst);

input [3:0]x; //4-bit input data

output [1:0]y; //2-bit output data

input clk; //clock

input rst; //reset

reg [1:0]y;

reg [3:0]ff0;

reg ff1,ff2;

always@(posedge clk, posedge rst)

begin

if(rst)

begin

y <= 2'b0;

ff1 <= 1'b0;

ff2 <= 1'b0;

ff0 <= x;

end

else

begin

ff1 <= ff0[0];

ff2 <= ff1;

y[0] <= (ff0[0]^ff2);

y[1] <= ff0[0]^ff1^ff2;

ff0 <= ff0 >>1;

end

end

endmodule-------------------------------------------------------------------------------------------------------------------

In the code x and y are the input and output. The input x is a 4 bit sequence and the output is a 2 bit sequence. clk and rst are clock and reset. The ff0, ff1 and ff2 are flip-flops. Within the always block the if-else procedural statement is applied such that first the reset(rst) is checked. If it is ON then output y, the flip-flop 1 and 2 are cleared and the input first bit is entered into the flip-flop 0. If it reset is not set then the first input entry is shifted into ff1, the content of ff1 into ff2, output y(0) and y(1) are calculated as y(0)= x(n)+x(n-2) and y(1)=x(n)+x(n-1)+x(n-2).

The corresponding Xilinx generated block diagram is shown below-

Tidak ada komentar:

Posting Komentar